= FPGA kriptografija=

Apibrėžimas:

„FPGA kriptografija“ yra kriptografijos mechanizmas naudojamas pasitelkiant FPGA lustus.

Paaiškinimas:

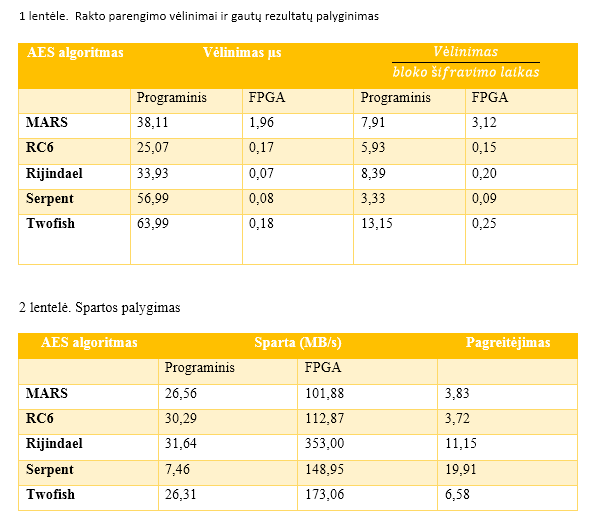

FPGA yra puiki alternatyva skirta privačių raktų kriptografijos algoritmams įgyvendinti. ASIC ( angl. application-specific integrated circuit) gali pasiekti geresnius spartos parametrus lyginant su FPGA, tačiau tai nesuteikia ASIC pranašumo, nes tokioms sistemoms trūksta lankstumo bei prisitaikymo prie esamos situacijos. ASIC tai yra technologija panaši į FPGA, tačiau pagrindiniai šių technologijų skirtumai yra tai, kad FPGA yra bendrojo naudojimo įterptinės sistemos pavyzdys, kai tuo tarpu ASIC yra specialiojo naudojimo sistemos pavyzdys. Be to programos įkėlimas gaminant ASIC sistemas yra labai brangus, todėl FPGA yra puikus sprendimas, jei reikalingas didesnis lankstumas, mažesnės išlaidos. Tačiau jei reikalinga sparta yra didesnė nei FPGA gali suteikti, tuomet ASIC yra nepakeičiamas variantas. Kita vertus jei palyginti programinę pusę, FPGA gali pasiūlyti labai aukštą spartą bei užtikrinti saugumą. FPGA didelis detalumas puikiai dera su privataus rakto kriptografiniais algoritmais ( pvz. bitų derinimo, bitų apkeitimo, look up lentelių skaitymo, boolio funkcijos) . Be to su FPGA galima įgyvendinti lygiagrečius algoritmų vykdymus, tai dar labiau paspartina sistemos darbą. Kaip spartaus darbo pavyzdys gali būti AES (angl. Advanced Encryption Standard) – pažangus šifravimo standartas. Lyginant FPGA šifravimo greitį su programiniu šifravimo greičiu FPGA spartesnė santykiu 1/15, kitais žodžiais tariant FPGA spartesnė 15 kartų už programinį AES modelį. Be to FPGA gali daug greičiau atlikti rakto turinio pakeitimus. Rakto turinio keitimas susideda iš duomenų, kurie priklauso nuo rakto, (key-dependent) generavimo kiekvienam kriptografijos etapui. Kriptografinis etapas gali prasidėti taip greitai kaip jo nuo rakto priklausanti informacija yra prieinama. Programiškai atliekamuose veiksmuose kriptografiniai procesai negali prasidėti tol kol visiems kriptografijos etapams duomenys nėra paruošti. Iš to išplaukia didelis vėlinimas ir raktų turinio keitimas yra neefektyvus. FPGA veikimas yra priešingas programiniam modeliui, kad kriptografija prasidėtų nereikia laukti kol visi duomenys bus paruošti. Dėl šios priežasties FPGA gaunami minimalūs vėlinimai. Kaip pavyzdys gali būti AES algoritmai, lyginant FPGA su programiniu kriptografijos modeliu, FPGA vėlinimai yra mažesni santykiu 20-700. Ir galiausiai saugumo klausimas padaro FPGA kriptografiją turinčią dar daugiau privalumų. Šifravimo algoritmai kurie veikia bendrojo pobūdžio kompiuteriuose neturi jokios fizinės apsaugos, kai tuo tarpu FPGA gali būti saugiai enkapsuliuota tam, kad būtų galima apsaugoti algoritmą nuo pakeitimų. Dėl visų šių saugumo privalumų FPGA ir kiti aparatiniai šifravimo mechanizmai yra naudojami karinėje pramonėje, kaip pavyzdys gali būti NSA (angl. National Security Agency) , jie patvirtina šifravimą tik ant aparatinių priemonių.

Naudota literatūra:

1.http://halcyon.usc.edu/~pk/prasannawebsite/papers/dandalisFCCM00.pdf

2.R. R. Taylor, S. C. Goldstein, “A High-Performance Flexible Architecture for Cryptography”, Workshop on Cryptographic Hardware and Embedded Systems